Los sistemas síncronos

Con frecuencia es necesario definir el ajuste y reinicio de operaciones que deben ocurrir en tiempos específicos. En un sistema no temporizado o sistema asíncrono, las salidas de las compuertas lógicas cambian su estado cada vez que una o varias entradas cambian. En un sistema temporizado o sistema síncrono, los tiempos exactos en los que alguna de las salidas cambia su estado están determinados por una señal de temporización o señal de reloj. Esta es en general un tren de pulsos rectangulares y cuando se usa la misma señal de reloj en todas las partes del sistema, las salidas están sincronizadas. La siguiente figura el apartado a) muestra este principio con compuertas en un flip-flop SR. 😀

|

| Flip-flop SR de reloj |

😏 La señal de ajuste y de reloj se suministran a través de una compuerta AND en la entrada S del flip-flop. Así, la señal de ajuste llega al flip-flop sólo cuando la señal de ajuste y la de reloj tiene valor 1.

Asimismo, la señal de reinicio junto con la señal de reloj entran a R a través de otra compuerta AND.

En consecuencia, el ajuste y el reinicio sólo pueden ocurrir en el momento definido por el temporizador.

La anterior figura 👆 el apartado b) muestra el diagrama de tiempos.

Flip-flop JK

💢 Para muchas aplicaciones no es aceptable el estado de indeterminación que se presenta con un flip-flop SR cuando S = 1 y R = l; por ello se emplea otro tipo de flip-flop: el flip-flop JK (ver figura siguiente).

|

| Flip-flop JK |

Este es un dispositivo flip-flop que se utiliza mucho.

La siguiente 👇 es la tabla de verdad de este dispositivo; observe que los únicos cambios de la tabla de estado flip-flop SR son las líneas cuando ambas entradas son 1.

|

| Tabla de la verdad del flip-flop JK |

Un ejemplo de aplicación de este flip-flop es la necesidad de obtener una salida con valor alto cuando la entrada A aumenta y después de cierto tiempo la entrada B aumenta. Para determinar si ambas entradas son altas se puede emplear una compuerta AND; sin embargo, su salida será alta sin importar cuál fue la entrada que aumentó primero. No obstante, si las entradas A y B se conectan a un flip-flop JK, A debe aumentar primero para que la salida aumente cuando B también aumente.

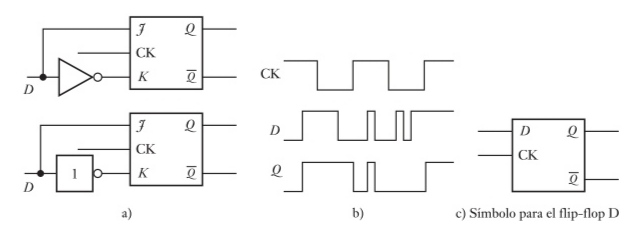

Flip-flop D

👊 El biestable de datos flip-flop D es de hecho un flip-flop SR con reloj, o un flip-flop JK cuya entrada D se conecta de manera directa a las entradas S o F y a través de una compuerta NOT a las entradas R o K ,como vemos en la figura siguiente en el apartado a); en el símbolo del flip-flop D, la entrada combinada R y K se denomina D.

|

| Flip-flop D |

De esta manera, una entrada 0 o de 1 conmuta la salida de manera que siga a la entrada D cuando el

pulso del reloj sea 1, como podemos observar en la figura anterior en el apartado b). Una aplicación particular del flip flop D es garantizar que la salida sólo tome el valor de la entrada D en tiempos definidos con precisión. En el apartado c) de la figura anterior se muestra el símbolo utilizado para un flip-flop D.

En el flip-flop D, cuando la entrada del reloj o la de activación aumenta, la. salida sigue a los datos presentados en la entrada D. Se dice que el flip-flop es transparente. Cuando se presenta una transición de alto a bajo en la entrada de activación, la salida Q se mantiene al nivel de datos justo anterior a la transición. Se dice que los datos en el punto de transición están latched (enclavados). Existen circuitos integrados de flip-flops D. Un ejemplo es el 7475, que contiene cuatro D transparentes latched.

La diferencia entre el flip-flop 7474 y el 7475 consiste en que el primero es un dispositivo de activación por flanco; en el paquete hay dos de estos flip-flops.

En un flip-flop D de activación por flanco, las transiciones de Q sólo ocurren en el flanco de entrada del pulso de reloj y en el 7474 en el flanco positivo, es decir, de la transición del nivel bajo a alto. La siguiente figura en el apartado a) se ilustra lo anterior.

|

| Flip-flop de activación por borde D |

a) Activación por borde positivo, b) símbolo para el flip-flop de activación por borde D.

💥 La diferencia entre el símbolo básico de un flip-flop D de activación por flanco y el de un flip-flop D es el pequeño triángulo que se coloca en la entrada del reloj CK (como podemos ver en la figura anterior en el apartado b)). También hay otras dos entradas denominadas preset y clear. Un valor bajo en la entrada del preset define la salida Q igual a 1, en tanto que un valor bajo en la entrada del clear borra la salida y hace Q igual a 0.

|

| Sistema de alarma |

Un ejemplo de una aplicación sencilla de este flip-flop se ve en la figura anterior, la cual muestra un sistema que sirve para que aparezca una luz verde cuando la entrada del sensor es baja y una luz roja cuando la entrada aumenta y hace sonar una alarma. La luz roja deberá permanecer encendida en tanto la entrada del sensor siga siendo alta, pero la alarma se puede apagar. Este podría ser el sistema para monitorear la temperatura de un proceso; acondicionamiento de señal producen una señal baja cuando la temperatura es inferior al nivel de seguridad y una señal alta cuando es superior a ese nivel.

👉 El flip-flop tiene una entrada alta. Cuando se aplica una entrada baja a la entrada CK y la entrada del sensor es baja, se enciende la luz verde. Cuando la entrada del sensor se vuelve alta, se apaga la luz verde, se enciende la roja y suena la alarma. Para eliminar la alarma se aplica una señal alta en la entrada CK, pero la luz roja permanece encendida mientras la entrada del sensor sea alta. Para construir este sistema se puede emplear un 7474 y un circuito o circuitos integrados que contengan tres compuertas NAND.

Escrito por Archie Tecnology

Buen articulo y muy bien explicado.

ResponderEliminar